Группа энтузиастов при участии компании Pixilica развивает проект RV64X, нацеленный на создание дополнительного набора инструкций для 3D-графики и обработки мультимедийных данных, который может использоваться для интеграции функциональности GPU в процессоры на базе архитектуры RISC-V. Проект позиционируется как свободный, не требующий отчислений и не налагающий условий на использование, что позволит создавать на базе RV64X полностью открытые GPU.

RV64X базируется на уже имеющихся в RISC-V ISA векторных инструкциях, которые расширены поддержкой новых типов данных и расширений, специфичных для обработки графики. Например, предложены дополнительные операции для обработки пикселей (RGBA), точек (XYZW), текстурных элементов (UVW-текселей), векторов (операции с 2-4 элементами), параметров материалов, расчёта освещения, трансцендентной математики, буферов глубины (Z-buffer) и кадровых буферов (Framebuffer). Первый прототип GPU на базе RV64X рассчитан на использование в микроконтроллерах и будет ограничен поддержкой графического API Vulkan. Со временем обещают добавить поддержку OpenGL и DirectX.

Основным мотивом разработки называется потребность в гибкой архитектуре, допускающей подключение расширений для эффективного решения специфичных задач, таких как двухфазовое усечение конусов, применение быстрых преобразований Фурье для произвольной глубины цвета и реализация аппаратных SLAM. Например, RV64X допускает реализацию собственных стадий для вычислительного конвейера, геометрических, пиксельных и кадровых буферов, а также создание собственных тесселяторов. При помощи RV64X производители чипов смогут подготовить необходимые для их задач решения на основе имеющегося костяка, сосредоточив внимание на расширенных возможностях, без необходимости тратить время на типовые вещи.

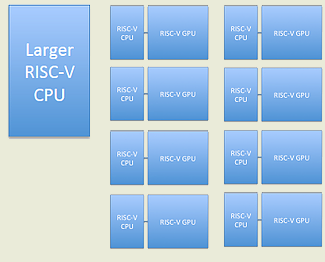

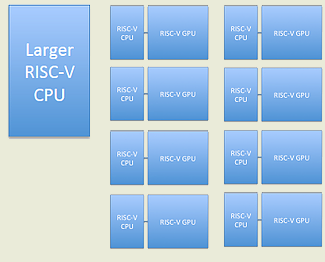

RV64X развивается как гибридный CPU-GPU ISA, позволяющий создавать как специализированные графические микроконтроллеры, так и многоядерные процессоры, комбинирующие вычислительные ядра с блоками для выполнения графических операций. Процессор, комбинирующий ядро RISC-V с блоком GPU, выглядит как единое целое (нет явного выделения GPU) и программируется с использованием унифицированного набора 64-разрядных инструкций и модели SIMD для обеспечения параллелизма на уровне данных. Архитектура RV64X развивается с оглядкой на компактную и эффективную реализацию, которая может быть воплощена в том числе на базе FPGA и ASIC.

Из особенностей архитектуры RV64X называется использование единой модели памяти в CPU и GPU, что позволяет обойтись без дополнительных механизмов RPC/IPC для трансляции вызовов между памятью GPU и CPU при обработке операций 3D API. Стандартные графические операции могут быть реализованы на уровне микрокода. Поддерживается создание пользовательских шейдеров, растеризаторов и расширений для трассировки лучей. Дополнительно на уровне микрокода могут быть реализованы векторные операции для решения задач симуляции, компьютерного зрения и машинного обучения.

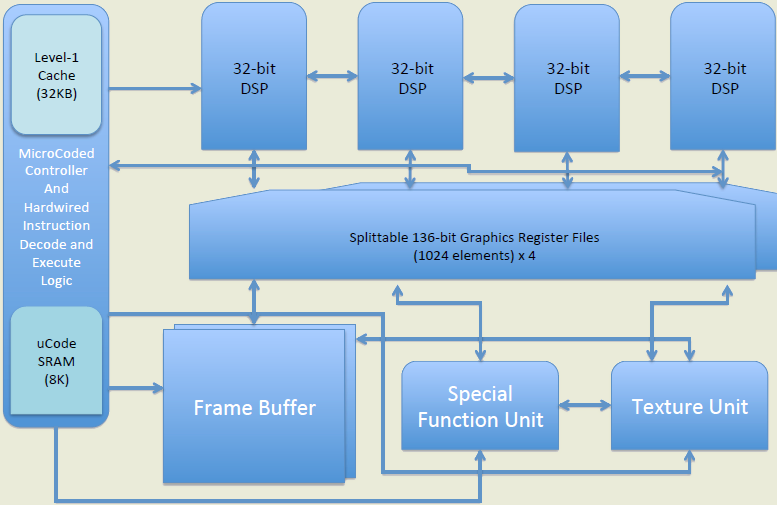

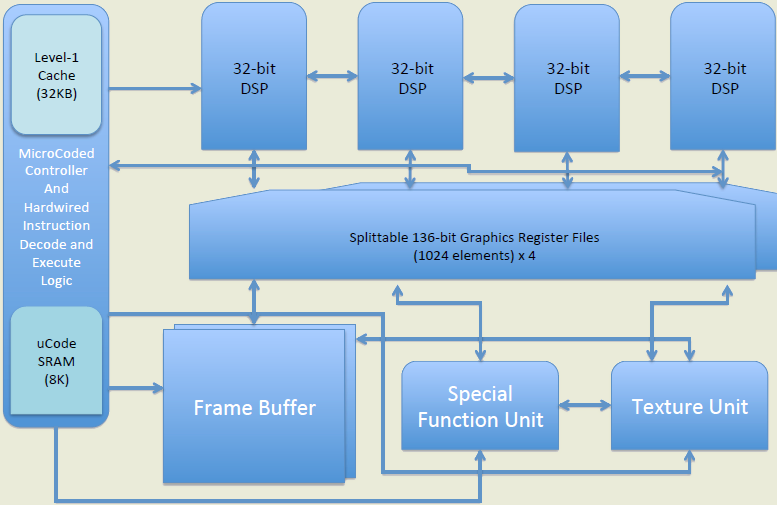

Эталонная реализация RV64X включает 32KB кэш первого уровня для инструкций и данных, 8 KB памяти SRAM для микрокода, декодировщик инструкций, аппаратную реализацию наборов инструкций RV32V и RV64X, задаваемый через микрокод декодировщик расширенных инструкций, векторное арифметико-логическое устройство (ALU), 136-разрядный регистровый файл с 1024 элементами, блок для выполнения специальных операций (SFU, Special Function Unit), блок обработки текстур (Texture Unit) и настраиваемый локальный фреймбуфер.

Источник статьи: https://www.opennet.ru/opennews/art.shtml?num=54501

RV64X базируется на уже имеющихся в RISC-V ISA векторных инструкциях, которые расширены поддержкой новых типов данных и расширений, специфичных для обработки графики. Например, предложены дополнительные операции для обработки пикселей (RGBA), точек (XYZW), текстурных элементов (UVW-текселей), векторов (операции с 2-4 элементами), параметров материалов, расчёта освещения, трансцендентной математики, буферов глубины (Z-buffer) и кадровых буферов (Framebuffer). Первый прототип GPU на базе RV64X рассчитан на использование в микроконтроллерах и будет ограничен поддержкой графического API Vulkan. Со временем обещают добавить поддержку OpenGL и DirectX.

Основным мотивом разработки называется потребность в гибкой архитектуре, допускающей подключение расширений для эффективного решения специфичных задач, таких как двухфазовое усечение конусов, применение быстрых преобразований Фурье для произвольной глубины цвета и реализация аппаратных SLAM. Например, RV64X допускает реализацию собственных стадий для вычислительного конвейера, геометрических, пиксельных и кадровых буферов, а также создание собственных тесселяторов. При помощи RV64X производители чипов смогут подготовить необходимые для их задач решения на основе имеющегося костяка, сосредоточив внимание на расширенных возможностях, без необходимости тратить время на типовые вещи.

RV64X развивается как гибридный CPU-GPU ISA, позволяющий создавать как специализированные графические микроконтроллеры, так и многоядерные процессоры, комбинирующие вычислительные ядра с блоками для выполнения графических операций. Процессор, комбинирующий ядро RISC-V с блоком GPU, выглядит как единое целое (нет явного выделения GPU) и программируется с использованием унифицированного набора 64-разрядных инструкций и модели SIMD для обеспечения параллелизма на уровне данных. Архитектура RV64X развивается с оглядкой на компактную и эффективную реализацию, которая может быть воплощена в том числе на базе FPGA и ASIC.

Из особенностей архитектуры RV64X называется использование единой модели памяти в CPU и GPU, что позволяет обойтись без дополнительных механизмов RPC/IPC для трансляции вызовов между памятью GPU и CPU при обработке операций 3D API. Стандартные графические операции могут быть реализованы на уровне микрокода. Поддерживается создание пользовательских шейдеров, растеризаторов и расширений для трассировки лучей. Дополнительно на уровне микрокода могут быть реализованы векторные операции для решения задач симуляции, компьютерного зрения и машинного обучения.

Эталонная реализация RV64X включает 32KB кэш первого уровня для инструкций и данных, 8 KB памяти SRAM для микрокода, декодировщик инструкций, аппаратную реализацию наборов инструкций RV32V и RV64X, задаваемый через микрокод декодировщик расширенных инструкций, векторное арифметико-логическое устройство (ALU), 136-разрядный регистровый файл с 1024 элементами, блок для выполнения специальных операций (SFU, Special Function Unit), блок обработки текстур (Texture Unit) и настраиваемый локальный фреймбуфер.

Источник статьи: https://www.opennet.ru/opennews/art.shtml?num=54501