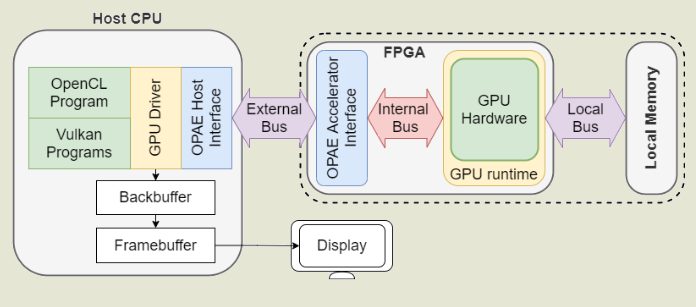

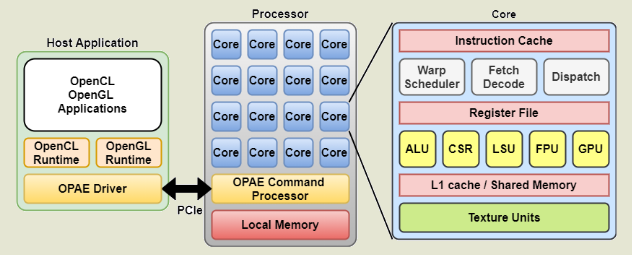

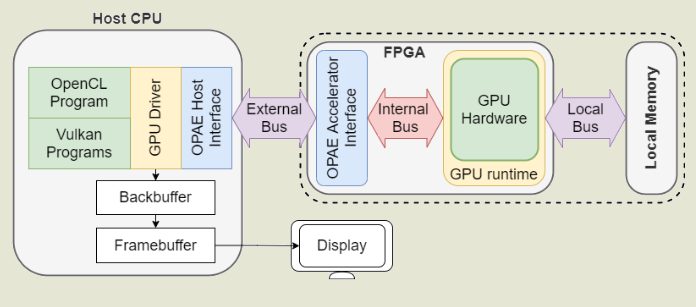

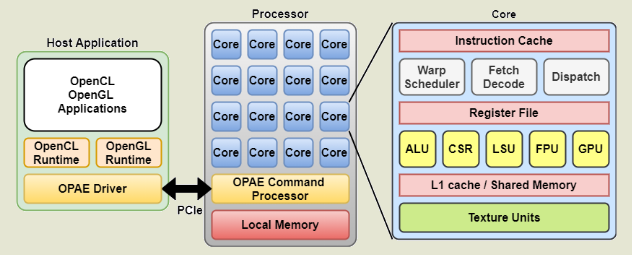

Группа исследователей из Технологического института Джорджии развивает исследовательский проект Vortex, предлагающий открытый GPGPU на базе архитектуры набора команд RISC-V, нацеленный на выполнение параллельных вычислений с использованием API OpenCL и модели выполнения SIMT (Single Instruction, Multiple Threads), а также на проведение исследований в области 3D-графики и разработки новых архитектур GPU. Проект пока находится на стадии прототипа, работающего при помощи FPGA. Схемы, описания аппаратных блоков на языке Verilog, симулятор, драйверы и сопутствующая проектная документация распространяются под лицензией BSD.

В текущем виде предоставляется типовой ISA RISC-V, расширенный некоторыми дополнительными инструкциями, необходимыми для поддержки функций GPU и управления потоками. При разработке авторы проекта попытались свести к минимуму изменения в архитектуре набора команд RISC-V, по возможности используя уже имеющиеся векторные инструкции. Похожий подход также применяется в проекте RV64X, который также развивает открытый GPU на базе технологий RISC-V.

Возможности Vortex по обработке графики пока ограничены. Заявлено о реализации поддержки OpenGL ES на базе Vortex, но в самом GPU пока реализована только инструкция "tex" для ускорения обработки текстур, которая выполняется на уровне фрагментного шейдера. Встроенный растеризатор отсутствует - все обработка геометрических операций выполняется на стороне системного CPU, а базовые примитивы для точек, линий и треугольников, а также обработка фрагментов, глубины и прозрачности, реализована с использованием ядра OpenCL.

В будущем планируется реализовать специфичные для обработки графики расширения ISA, добавить поддержку API CUDA и Vulkan, а также расширения для ускорения систем машинного обучения и анализа данных. Для разработки приложений предлагается инструментарий, включающий адаптированные для работы с Vortex варианты PoCL (компилятор и runtime OpenCL), LLVM/Clang, GCC и Binutils. Поддерживается симуляция работы чипа с использованием Verilator (Verilog-симулятор) и SimX (программная симуляция).

Основные особенности Vortex:

В текущем виде предоставляется типовой ISA RISC-V, расширенный некоторыми дополнительными инструкциями, необходимыми для поддержки функций GPU и управления потоками. При разработке авторы проекта попытались свести к минимуму изменения в архитектуре набора команд RISC-V, по возможности используя уже имеющиеся векторные инструкции. Похожий подход также применяется в проекте RV64X, который также развивает открытый GPU на базе технологий RISC-V.

Возможности Vortex по обработке графики пока ограничены. Заявлено о реализации поддержки OpenGL ES на базе Vortex, но в самом GPU пока реализована только инструкция "tex" для ускорения обработки текстур, которая выполняется на уровне фрагментного шейдера. Встроенный растеризатор отсутствует - все обработка геометрических операций выполняется на стороне системного CPU, а базовые примитивы для точек, линий и треугольников, а также обработка фрагментов, глубины и прозрачности, реализована с использованием ядра OpenCL.

В будущем планируется реализовать специфичные для обработки графики расширения ISA, добавить поддержку API CUDA и Vulkan, а также расширения для ускорения систем машинного обучения и анализа данных. Для разработки приложений предлагается инструментарий, включающий адаптированные для работы с Vortex варианты PoCL (компилятор и runtime OpenCL), LLVM/Clang, GCC и Binutils. Поддерживается симуляция работы чипа с использованием Verilator (Verilog-симулятор) и SimX (программная симуляция).

Основные особенности Vortex:

- Поддержка архитектуры набора команд RISC-V RV32IMF.

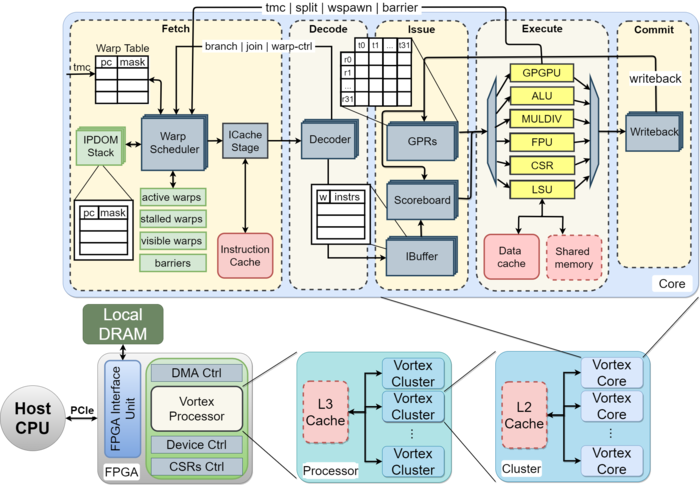

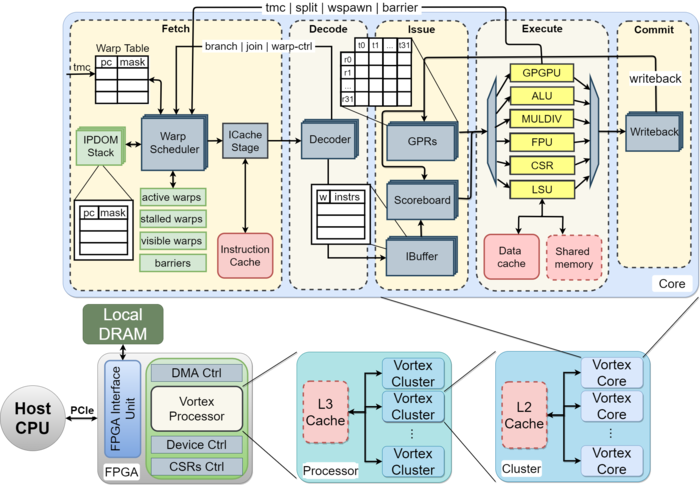

- Масштабирование чипа до 64 ядер с опциональными кэшами L2 и L3.

- Каждое ядро может выполнять 1024 потоков и работать с частотой 250 MHz.

- Максимальная вычислительная мощность оценивается в 128 Gflops, а пропускная способность памяти 16 GB/s. 32-ядерная реализация, работающая с частотой 200 Mhz, на базе FPGA Altera Stratix 10 показала производительность в 25.6 GFlops.

- Поддержка стандарта OpenCL 1.2.

- Возможность реализации на базе FPGA Intel Arria 10 и Intel Stratix 10.